## Seminararbeit Der Pentium Division-Bug

Seminar: Berühmt berüchtigte Softwarefehler Seminarleitung: Dr. Bernhard Beckert

Verfasser: Sebastian Knieschewski

08. Januar 2004

# Inhaltsverzeichnis

| 1         |                                                                 |                |  |  |  |  |  |

|-----------|-----------------------------------------------------------------|----------------|--|--|--|--|--|

| 2         |                                                                 |                |  |  |  |  |  |

| 3         | Der Pentium Prozessor3.1 Intel Pentium P53.2 Intel Pentium P54C | <b>6</b> 6 8   |  |  |  |  |  |

| 4         | Der Divisions-Fehler im Pentium Prozessor                       |                |  |  |  |  |  |

| 5         | Der SRT-Divisionsalgorithmus                                    | 11             |  |  |  |  |  |

| 6         | Workarounds für den Divisionsfehler                             |                |  |  |  |  |  |

| 7         | Reaktionen der Öffentlichkeit und Geschäftspartner              |                |  |  |  |  |  |

| 8         | Intels Konkurrenz 8.1 AMD                                       | 17<br>17<br>18 |  |  |  |  |  |

| 9         | Intels Konsequenzen 9.1 Umtausch                                | 19<br>19<br>19 |  |  |  |  |  |

| 10        | Verifikation                                                    | 21             |  |  |  |  |  |

| 11        | Schaden                                                         | 22             |  |  |  |  |  |

| <b>12</b> | Fazit                                                           | 23             |  |  |  |  |  |

| 13        | Literatur                                                       | 24             |  |  |  |  |  |

## Abstrakt

Die folgende Arbeit beschreibt die Entwicklung von Prozessoren, insbesondere der Intel Prozessoren, bis hin zum Pentium Prozessor. Die einzelnen Funktionseinheiten des Pentium Prozessors werden grob skizziert. Das besondere Augenmerk schließlich gilt der Darstellung des im Koprozessor der CPU aufgetretenen Divisions-Fehlers, dessen öffentlicher Entdeckung sowie der Erläuterung dessen technischer Ursachen und wirtschaftlicher Folgen. Der Ursprung des Fehlers liegt in einer unvollständig übertragenen Divisionstabelle, auf die der SRT-Divisionsalgorithmus zurückgreift, und die dem Koprozessor falsche Werte zur Berechnung liefert. Der Divisions-Fehler im Pentium war die bisher größte von der Öffentlichkeit erzwungene Rückrufaktion.

#### Intel

Die Intel Corporation wurde 1968 von Robert Noyce und Gordon Moore gegründet. Der Schwerpunkt der Entwicklung und Produktion lag bei Halbleiter-Speichersystemen. Im November 1971 brachte Intel seinen ersten Mikroprozessor auf den Markt, den 4004i. Er besaß 2.300 Transistoren und hatte einen 4 Bit breiten Datenbus und einen 12 Bit breiten Adressbus mit dem insgesamt 4 KByte Speicher adressiert werden konnte. Der Prozessor war mit 108 KHz getaktet. Aber erst im Juni 1978 konnte Intel sich mit dem 8086 auf dem Prozessormarkt behaupten. Es war der erste 16 Bit Prozessor, also mit einem 16 Bit Datenbus. Der Adressbus verfügte über 20 Bit Breite und konnte bis zu 1 MByte Speicher adressieren. Der 8086er verfügte über 29.000 Transistoren und konnte mit 4,77, 8 und 10 MHz getaktet werden.<sup>2</sup> Der kleine Bruder des 8086er, der 8088er wurde dann von IBM in den ersten Personal Computer verbaut, in den IBM XT (eXtended Technology). Der 8088er unterschied sich zu dem 8086er nur in der Datenbusanbindung. Intel war mit der im 8086er verwendeten 16 Bit Technologie seiner Zeit regelrecht vorraus und die Entwicklung von 16 Bit Plattformen für den Prozessor war langsam und die Endprodukte waren sehr teuer. Deshalb entwickelte Intel den 8086er so um, dass er Kompatibel mit den alten 8-Bit-System war und auch dort eingesetzt werden konnte. So war der Datenbus intern im 8088er immer noch 16 Bit breit, nur die externe Anbindung an die Systemplatinen war auf 8 Bit reduziert. Das bremste die CPU (Central Processing Unit) aus, aber sie war noch immer weit schneller als die bisherigen 8-Bit-Prozessoren.<sup>4</sup>

Schon in den 80er Jahren wurde die asiatische Konkurrenz im Bereich der Speicherproduktion und Entwicklung so stark, dass Intel sowohl preislich als auch qualitativ unter Druck geriet. Die japanischen und koreanischen Speicherhersteller produzierten bessere, schnellere und günstigere Speicherchips mit denen sie auch auf den amerikanischen Markt drängten. Intels Produktivität bei den Speicherchips war zu gering um konkurrenzfähig zu bleiben und nachdem Intel im März 1991 bei einem internationalen Vergleich mit Konkurrenten aus

$<sup>^1{\</sup>rm vgl.}$  Jackson, T., 1998: Inside Intel - Die Geschichte des erfolgreichsten Chip- Produzenten der Welt, Hamburg, Hoffmann und Campe Verlag, Seite 90 ff.

$<sup>^2{\</sup>rm vgl.}$  www.bigtom.ch , 2003: CPU-Chronik, online im Internet unter: http://www.bigtom.ch/CPUs/index5.htm [letzter Zugriff: 14.06.2003]

<sup>&</sup>lt;sup>3</sup>vgl. Gardner, A., 1993: Beck EDV-Berater im dtv - Basiswissen: PC-Hardware - Rechner

- Tastatur - Maus - Bildschirm - Disketten, 2. Auflage, München, Verlag C.H. Beck Seite 40,41

<sup>4</sup>vgl. Jackson, T., 1998, a.a.O., Seite 245 ff.

dem ostasiatischen Raum regelrecht deklassiert wurde, zog sich Intel bald aus der Speicherproduktion zurück. Dies aber auch nur, weil die Herstellung von  ${\rm CPUs}$  mittlerweile einen sehr hohen Gewinn erwirtschaftete.  $^5$

Bei der Entwicklung neuer Prozessorgenerationen wurde bei Intel stets darauf geachtet die Prozessoren abwärtskompatibel zu halten. Damit wurde die allgemeine Akzeptanz neuer Prozessoren gesteigert, da zwar noch immer neue Plattformen bzw. Motherboards für die neuen Prozessoren entwickelt werden mussten, aber nicht die Software, die für eine vorherigen Prozessorgeneration geschrieben wurde, umgeschrieben werden musste. Also konnte die alte Software problemlos auf neuen Systemen weiterverwendet werden, aber auch zugleich mit neuer Software alle Leistungspotentiale der neuen Funktionen in der CPU ausgeschöpft werden. So kam es, dass bei jeder neuen Prozessorgeneration immer der alte Instruktionssatz wiederverwendet wurde und nur einige Befehle hinzugefügt wurden, die dann durch neue für die entsprechende Prozessorgeneration optimierte Software genutzt werden konnte. Zusätzlich wurden sowohl von Intel als auch von vielen anderen Halbleiterherstellern Coprozessoren bzw. FPUs (Floating Point Unit) entwickelt, die speziell für die Berechnung von Fließkommazahlen entwickelt wurden.<sup>6</sup> Der Hauptprozessor kann bisher nur Integer-Zahlen berechnen. Bei der Fließkommaberechnung mußder Hauptprozessor die Fließkommazahlen in Integer-Zahlen umwandeln, berechnen und wieder zurück umwandeln. Da der Coprozessor direkt mit den Fließkommazahlen rechnen kann ist dieser bis zu 100 mal schneller bei diesen Berechnungen. Die CPU übergibt solche Berechnungen direkt an den Coprozessor, wenn er im System vorhanden war.<sup>7</sup> Die Bezeichnungen der Intel Coprozessoren waren analog zu den Prozessorgenerationen 8087, 80287, 80387 und 80487; ab dem 80486 Prozessor war der Coprozessor im Hauptprozessor integriert, aber Intel lieferte die CPUs mit fehlerhaften Coprozessor als 80486-SX aus, in dem der Coprozessor enthalten war, aber deaktiviert war, weil er nicht funktionierte oder fehlerhaft war. Deshalb gab es für den 80486 auch noch Coprozessoren die für die 80486-SX Varianten nachgerüstet werden konnten.<sup>8</sup> Ab 1997 entwickelte Intel einen gesonderter Befehlssatz für Multimediaanwendungen, den MMX-Befehlssatz (MultiMedia EXtension). Auch dieser wurde in den folgenden Prozessorgenerationen weiterentwickelt und es kamen immer mehr solcher speziellen Instruktionssätze in den CPUs dazu.

<sup>&</sup>lt;sup>5</sup>vgl. Jackson, T., 1998, a.a.O., Seite 360

$<sup>^6 {\</sup>rm vgl.}$ Bernstein H., 1991: PC-TUNING Vom Standard-PC zum Personal-Super-Computer, München: Markt & Technik Verlag, Seite 99 ff.

<sup>&</sup>lt;sup>7</sup>vgl. Gardner, A., 1993, a.a.O., Seite 111 f.

$<sup>^8\,\</sup>mathrm{vgl}.$  Dr. Dobb's Journal, 2003: PC Processors Guide by x86.org, online im Internet unter: <code>http://x86.ddj.com/articles/computalk/help.htm</code> [letzter Zugriff: 07.05.2003]

9

| IntEinheit | Instruktionen | Adressiermodi | Einheit  | Instruktionen | Adressiermod |

|------------|---------------|---------------|----------|---------------|--------------|

| 8086       | 92            | 49 000        | MMX      | +47           | 1 880 000    |

| 80186      | +8            | 51 000        | MMX2     | +18           | 2 310 000    |

| 80286      | +16           | 53 000        | MMX3     | +3            | 2 420 000    |

| 80386      | +54           | 8 600 000     | SSE      | +28           | 1 250 000    |

| 80486      | +8            | 9 200 000     | SSE2     | +99           | 5 000 000    |

| Pentium    | +8            | 9 300 000     | M-Stream | +10           | 78 000       |

| P6         | +16           | 10 500 000    | FPU      | +68           | 5700         |

| PII        | +2            | 10 500 000    | FPU387   | +6            | 278 000      |

| P4         | +0            | 10 500 000    | FPUP6    | +11           | 278 000      |

Aktuelle CPUs, wie der Intel Pentium IV, oder das Konkurrenzprodukt, der AMD Athlon XP, besitzen mittlerweile über 55 Millionen Transistoren und besitzen mehrere zusätzliche Instruktionseinheiten, wie sie in der obigen Abbildung genannt sind. Die Entwicklung solcher speziellen Instruktionssätze lag meist bei Intel und die Konkurrenz musste meist teure Lizenzen erwerben, um diese Instruktionssätze auch in die eigenen Prozessoren einbinden zu dürfen. So ist im aktuellen AMD Athlon XP der MMX und SSE Instruktionssatz von Intel eingebunden, daneben hat AMD natürlich mittlerweile auch eigene Instruktionssätze entwickelt (3D now! und die entsprechenden Weiterentwicklungen), die aber bei weitem eine nicht so hohe Akzeptanz bei den Softwareherstellern erfahren wie die Instruktionssätze von Intel. Denn solange die speziellen Mikrobefehle, die durch solche Instruktionssätze der CPU hinzugefügt werden, nicht von der Software genutzt werden, profitiert die Software nicht von diesen Erweiterungen der CPU.<sup>10</sup>

<sup>&</sup>lt;sup>9</sup>c't Magazin fur Computer und Technik, Ausgabe 13/2003, S.94

$<sup>^{10}\,\</sup>rm vgl.$  Gelsinger, P.P. , 2003: For ever young. Die Intel-Architektur: 25 Jahre Innovation und kein Ende abzusehen, in: c't Magazin fur Computer und Technik, Ausgabe 13/2003, S. 92 - 95

## Der Pentium Prozessor

#### 3.1 Intel Pentium P5

Intel Pentium Prozessor mit 60MHz  $^{11}$

Der Intel Pentium Prozessor wurde von Intel erstmals in der 36. Kalenderwoche 1993 ausgeliefert. Die verfügbaren Taktraten für den Pentium beschränkten sich, abgesehen von einigen Testmustern mit 50 MHz, auf 60 und 66 MHz. <sup>12</sup> Diese Taktfrequenzen waren zum Zeitpunkt des Erscheinens der Pentium CPU nicht sehr hoch, da auch CPUs der 486er Baureihe mit 50 und 66 MHz getaktet wurden. Trotzdem war die Pentium CPU bis zu doppelt so schnell wie ein gleichgetakteter 486er Prozessor. Das lag zum Teil an der höheren Anzahl von Transistoren, 3,1 Millionen im P5<sup>13</sup> gegenüber 1,25 Millionen im P4, der 486er Baureihe mit integrierten Koprozessor und Taktraten von 20 bis 50 MHz, die in der Pentium CPU verbaut wurden. Viel mehr Geschwindigkeit brachten neue Technologien, die in die Pentium CPU implementiert wurden. Die zwei Schlüsseltechnologien zum Beschleunigen der Pentium CPU waren das Branch

$<sup>^{11}\</sup>mathrm{CPU} ext{-}\mathrm{Abbildung}$  aus eigener Sammlung

$<sup>^{12}\</sup>mathrm{vgl}.$  Intel Corporation, 1997 a: 60- and 66-MHz Pentium Processor Specification Update. Order Number: 243326-001, online im Internet unter: http://www.intel.com/design/intorch/specupdt/fhb.pdf [letzter Zugriff am 27.08.2003]

<sup>&</sup>lt;sup>13</sup>vgl. CPU-Museum, 2002 - 2003 b: Intel Pentium P5, online im Internet unter: http://www.cpu-museum.de/?m=Intel&f=Pentium+P5 [letzter Zugriff: 30.08.2003]

Prediction und die Superskalare Architektur. 14

Das Branch Prediction ist ein Algorithmus, der versucht if-then-else- Verzweigungen im Programmcode vorherzusagen. Dadurch dass der Pentium Prozessor mehr oder weniger schon im vorraus wußte welche Verzweigung gewählt werden würde, konnte er die entsprechend folgenden Instruktionen schon vorab berechnen und mußte nicht erst warten, bis das Programm an der Verzweigung im Code angekommen war. D.h. der Prozessor hatte weniger Leerlaufzeiten und konnte viele Zeilen im Code vorab verarbeiten. Der Branch-Prediction-Algorithmus arbeitet mit einer Tabelle in der bisher gewählte Verzweigungen gespeichert wird. Eine simple Annahme des Algorithmus ist zum Beispiel, dass, wenn eine Verzweigung zweimal auftaucht, auch zwei mal der gleiche Weg gewählt wird. Wenn der Prozessor die falsche Wahl für das Ergebnis der Verzweigung getroffen hatte, hatte der Prozessor natürlich einige Zeit an etwas gerechnet, was völlig nutzlos war, aber es bestand immerhin eine 50 zu 50 Chance das Richtige zu berechnen. Dieses Verfahren erwies sich als effektiver als den Prozessor einfach warten zu lassen. Eine maximale Auslastung oder minimale Leerlaufzeiten der CPU bedeutet zugleich auch, dass die maximale Verarbeitunsgeschwindigkeit erreicht werden kann. Je nach Anwendung, war der Branch Prediction Algorithmus in der Lage zwischen 50 und 80% aller if-then-else Verzweigungen richtig zu "raten". 15 Die Superskalare Architektur ermöglichte, mehrere Verarbeitungsschritte in einem Taktzyklus zu bewältigen und einige Arbeitsschritte unabhängig voneinander durchzuführen. So konnte die Befehls-Pipeline als auch die FPU voneinander unabhängig Daten parallel verarbeiten. Zusätzlich war die FPU in der Lage zwei Integer-Instruktionen in einem Taktzyklus und bei einigen Fließkommaberechnungen zwei Instruktionen in einem Taktzyklus, zu verarbeiten. 16

Die dritte Komponente, die die Pentium CPU erheblich beschleunigte, war der auf dem Prozessor integrierte Cache-Speicher, der im vollen Prozessortakt lief. Der Cache Speicher bestand jeweils aus einem 8KB großen Instruktions-Cachespeicher und einem 8KB großen Daten-Cachespeicher. Cachespeicher, integriert auf der CPU, wurde zwar bereits bei dem 486er und auch einigen 386ern verwendet, wurden aber nun nach den Praxis-Erfahrungen besonders aus dem 486er optimiert. Außerdem wurde eine zweite Cache-Instanz auf dem Motherboard verwendet, die zwar auch schon auf 486er-Boards verwendet wurde, nun aber größer und schneller war. Der P5 Pentium Prozessor wurde mit dem sogenannten Sockel 4 mit dem Motherboard verbunden. Der Sockel 4 war nicht pinkompatibel zu seinem Vorgänger, dem Sockel 3 für die 486er, und so konnten Pentium CPUs nur in Verbindung mit neuen Motherboards betrieben werden. Die neuen Motherboards hatten zumeist auch die damals neue PCI-Technologie (Periphal Component Interface) für eine schnellere Verbindung zwischen Systembus und Peripheriegeräten.<sup>17</sup>

$<sup>^{14}\</sup>mathrm{vgl}.$  Intel Corporation, 1997 b: Pentium Processor, online im Internet unter: http://developer.intel.com/design/pentium/datashts/24199710.pdf [letzter Zugriff: 17.02.2004]

$<sup>^{15} \</sup>rm vgl.$  Fog, A., 2003: Branch prediction in the Pentium family, online im Internet unter: http://x86.ddj.com/articles/branch/branchprediction.htm [letzter Zugriff: 01.07.2003]

<sup>&</sup>lt;sup>16</sup>vgl. Intel Corporation, 1997 b, a.a.O.

$<sup>^{17}</sup>$ vgl. CPU-Museum, 2002 - 2003 b, a.a.O.

#### Intel Pentium P54C 3.2

Intel Pentium Prozessor mit 75MHz & Intel Pentium Prozessor mit 100MHz<sup>18</sup>

Der Nachfolger des P5 war der weiterentwickelte Pentium Prozessor P54C. Er wurde erstmal im März 1994 ausgeliefert und wurde zuerst mit 75 MHz getaktet, und später dann auch mit 90, 100, 120, 133, 150, 166 und 200 MHz. Die P54C CPUs besaßen 3,2 bis 3,3 Millionen Transistoren und waren erstmals dualprozessorfähig. Damit war es möglich, zwei Prozessoren auf einem Motherboard betreiben zu können, was nahezu eine Verdoppelung der Arbeitsgeschwindigkeit ermöglichte. Der P54C war nicht pin-kompatibel mit dem P5 und hatten dementsprechend einen eigenen Sockel-Standard 5. Gegenüber dem P5 hatte der P54C den Vorteil, weniger Spannung zu benötigen, was eine geringere Wärmeentwicklung der CPU zur Folge hatte und erst das Erreichen von Taktfrequenzen bis zu 200 MHz ermöglichte. Der P54C arbeitete mit 3,3V, wogegen der P5 noch 5V zum Betrieb benötigte. 19

<sup>18</sup> CPU-Abbildungen aus eigener Sammlung

19 vgl. CPU-Museum, 2002 - 2003 c: Intel Pentium P54C, online im Internet unter: http://www.cpu-museum.de/?m=Intel&f=Pentium-S+%2F+P54C [letzter Zugriff: 30.08.2003

# Der Divisions-Fehler im Pentium Prozessor

Dr. Thomas R. Niceley war Mathematik-Professor am Lynchburg College und berechnete große Primzahlpaare und die Zahl  $\pi$ . Er hatte viele Berechnungen jahrelang auf 486ern laufen lassen und bemerkte nun, als er auch einige Pentium-Systeme zur Berechnung verwendete, unterschiedliche Ergebnisse, wenn er neuere Berechnungen mit alten verglich. Nur auf Systemen mit Pentium Prozessoren traten die Fehler bei Divisionen mit vielen Nachkommastellen auf. Als er die unterschiedlichen Ergebnisse fand, hatte er keine Ahnung, wo der Fehler liegen konnte und suchte daher anfangs in seinem eigenen Programm nach möglichen Fehlern. Da er mit dem gefundenen und korrigierten Fehlern noch immer nicht auf das Ergebnis seiner alten Berechnungen kam, suchte er den Fehler im Compiler. Er versuchte, alle Optimierungen soweit wie möglich herauszunehmen, um diese als Fehlerquellen ausschließen zu können. Als aber auch diese Maßnahme keine Verbesserung brachte, vermutete R. Nicely erstmals den Fehler in der Hardware. Er vermutete den Fehler in dem ebenfalls neu eingeführten PCI-Bus auf den Pentium-Systemen, konnte dort aber nicht den Fehler ausschließen, da die PCI-Technologie noch sehr neu war und dementsprechend schlecht bis gar nicht öffentlich dokumentiert war. Mit Rücksprache zu einigen Systementwicklern, schob er das Problem mit dem PCI-Bus auf, bzw. ging davon aus, dass dort nicht der Fehler liegen könnte. Die einzige Fehlerquelle war nun nur noch die CPU selber. Am 19. Oktober 1994 entdeckte R. Niceley dann schließlich, dass er den Fehler beheben konnte, indem er den mathematischen Koprozessor der Pentium CPU deaktivierte. Nachdem er sein Ergebnis auf insgesamt fünf anderen unterschiedlichen Pentium-Systemen, sowohl mit dem P5 als auch mit dem P54C Pentium Prozessoren überprüft hatte und der Fehler immer wieder auftauchte, meldete er am 24. Oktober 1994 seine Entdeckung Intel. R. Niceley rief die Kundenhotline an und teilte dem Intel-Mitarbeiter den Fehler mit. Der Intel-Mitarbeiter, dessen Name nie veröffentlicht wurde, nahm die Beanstandung zwar entgegen und versprach R. Niceley eine Antwort, aber diese erfolgte nie. Als R. Niceley mehrere Wochen später noch immer keine Antwort erhalten hatte, wendete er sich per E-Mail an mehrere Institute und Privatpersonen, die von diesem Fehler ebenfalls betroffen sein konnten und sich für diesen interessieren könnten. Schnell stellte sich heraus, dass womöglich alle Pentium Prozessoren diesen Fehler hatten und es wurden Zahlen gefunden, mit deren Division sich der Fehler eindeutig zeigte. So ergab die Division der Zahl 824.633.702.441 durch sich selber nicht 1, sondern 0,99999996274709702! Da der Fehler mittlerweile in mehreren Newsforen diskutiert wurde, stellte sich schnell heraus, dass zum Beispiel die Division aller Zahlen zwischen 824.633.702.418 und 824.633.702.449 durch sich selber nicht 1 ergaben. Aber auch viele andere Berechnungen ergaben falsche Ergebnisse, wobei der Fehler sich frühestens ab der neunten Nachkommastelle zeigte.<sup>20</sup>

Erst als die Kritik in den News-Foren (besonders in comp.sys.intel) immer lauter wurde und auch mittlerweile die Fachpresse über den Fehler berichtete, bestätigte Intel am 28. November 1994 offiziell den Fehler. Damit einhergehend wurde ein Austausch bei Bedarf angeboten. D.h. Intel würde nur dann den Pentium Prozessor austauschen, wenn der Kunde nachweisen könne, dass er komplexe Berechnungen durchführe, bei denen der Fehler auftreten könne. In dem von Intel veröffentlichten Whitepaper wurde eine Statistik angegeben, nach der der Divisions-Fehler bei der Verwendung von Microsoft Windows und Textverarbeitungsprogrammen wie Microsoft Word, Wordperfect und ähnlichen nie auftreten würde. Bei der Verwendung von Tabellenkalkulationsprogrammen wie Microsoft Excel oder QuattroPro würde der Fehler etwa alle 27.000 Jahre einmal auftreten.<sup>21</sup>

| Class                        | Applications                                                                                          | MTBF         | Impact of failure<br>in div/rem/tran |

|------------------------------|-------------------------------------------------------------------------------------------------------|--------------|--------------------------------------|

| Word processing              | Microsoft Word, Wordperfect, etc.                                                                     | Never        | None                                 |

| Spreadsheets<br>(basic user) | 123, Excel, QuattroPro<br>(basic user runs fewer than 1000 div/day)                                   | 27,000 years | Unnoticeable                         |

| Publishing,<br>Graphics      | Print Shop,<br>Adobe Acrobat viewers                                                                  | 270 years    | Impact only on Viewing               |

| Personal Money<br>Management | Quicken, Money, Managing Your Money,<br>Simply Money, TurboTax<br>(fewer than 14,000 divides per day) | 2,000 years  | Unnoticeable                         |

| Games                        | X-Wing, Falcon (flight simulator), Strategy<br>Games                                                  | 270 years    | Impact is benign,<br>(since game)    |

Intel war intern der Fehler schon einige Monate bekannt gewesen, man hatte gehofft, dass er den Benutzern der Pentium CPUs nicht auffallen würde, da er tatsächlich relativ selten auftrat. Nun versuchte Intel die Auswirkungen des Fehlers mit der veröffentlichten Statistik herunterzuspielen und zu behaupten, der Fehler würde bei einem durchschnittlichen Benutzer quasi nie auftreten.<sup>23</sup>

<sup>&</sup>lt;sup>20</sup>vgl. Jackson, T., 1998, a.a.O., Seite 420 ff.

$<sup>^{21} {\</sup>rm vgl.}$  Intel Corporation, 1994: Statistical Analysis of Floating Point Flaw in the Pentium Processor (Dateiname: Intel white.ps), in: pentium.zip, Download unter: http://www.mathworks.com/matlabcentral/fileexchange/ loadFile.do?objectId=1666&objectType=file [letzter Zugriff: 15.06.2003]

$<sup>^{22} \</sup>mathrm{Intel}$  Corporation, 1994, a.a.O.

<sup>&</sup>lt;sup>23</sup>vgl. Jackson, T., 1998, a.a.O., Seite 422 ff.

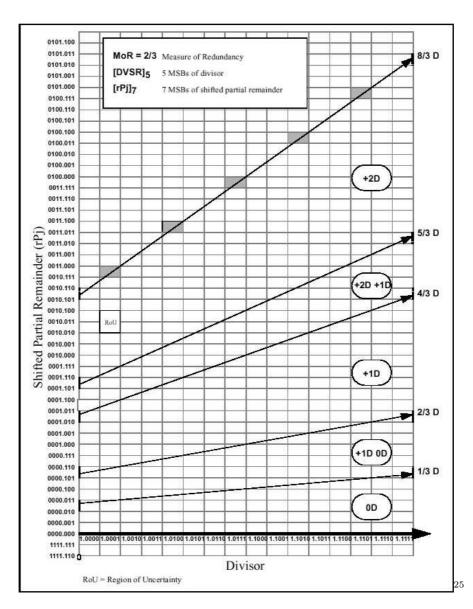

# Der SRT-Divisionsalgorithmus

Der neue Divisionsalgorithmus im Pentium hatte den Vorteil, dass er zwei Nachkommastellen in einem Zyklus berechnen konnte. Der SRT-Divisionsalgorithmus (benannt nach den drei Entwicklern des Verfahrens Sweeny, Robinson und Tocher) greift dabei auf eine Matrix zurück, aus der er entsprechende Werte ausliest und damit das Ergebnis berechnen kann. Diese Matrix besteht aus 2048 Zellen von denen 1066 beschrieben sein sollten. 5 der 1066 Zellen waren aber fehlerhaft und wenn auf eine dieser 5 Zellen zrückgegriffen wurde, dann entstand der Fehler in der Division.

Die fehlerhaften Werte liegen alle am oberen Rand der beschriebenen Werte in der Matrix. Der SRT-Divisionsalgorithmus greift aber gerade auf diese Zelle eher selten zu, weshalb der Divisionsfehler im Pentium Prozessor so selten auftritt.  $^{24}$

<sup>&</sup>lt;sup>24</sup>vgl. Halfhill, T.R., 1995: The Truth Behind The Bug, online im Internet unter: http://www.byte.com/art/9503/sec13/art1.htm [letzter Zugriff: 03.07.2003]

Der eigentliche Fehler liegt aber gar nicht in der Tabelle, sondern schon im dem Programm, das zur Übertragung der Werte in die Tabelle, die auf der PLA (Programmable Logical Area) im Prozessor gespeichert ist, in der Programmiersprache C enwickelt wurde. Das Programm benutzte eine einfache FOR-Schleife, um die Zellen in der Matrix zu beschreiben und genau an den fünf fehlerhaften Stellen hätte der Wert "2" übertragen werden sollen. Wegen der falsch programmierten FOR-Schleife wurden diese Zellen stattdessen gar nicht beschrieben und hatten damit den Wert "0", da die gesamte Tabelle vorab mit Nullen belegt war. <sup>26</sup>

So entstand der Divisionsfehler in der Hardware des Pentium Prozessors durch eine falsch programmierte FOR-Schleife. Wer bei Intel für die Program-

<sup>&</sup>lt;sup>25</sup>Intel Corporation, 1994, a.a.O.

<sup>&</sup>lt;sup>26</sup>vgl. Halfhill, T.R., 1995, a.a.O.

mierung dieses Programms zuständig war, und ob das Programm auf Richtigkeit überprüft worden war, hat Intel natürlich nie veröffentlicht. Anzunehmen ist aber, dass bei der gesamten Entwicklung oft nicht sehr sorgfältig gearbeitet wurde, da der Leistungsdruck innerhalb Intels sehr hoch war. Dieser Leistungsdruck war aber weniger auf die Qualität der Produkte gesetzt, sondern eher auf die möglichst schnelle Fertigstellung des Produktes.<sup>27</sup>

<sup>&</sup>lt;sup>27</sup>vgl. Jackson, T., 1998, a.a.O.

# Workarounds für den Divisionsfehler

Da sich Intel lange Zeit nicht sehr kooperativ zeigte, wurden in den Newsforen Möglichkeiten diskutiert, die den Fehler in der CPU umgehen können. Insgesamt wurden drei Möglichkeiten gefunden, den Fehler in der CPU zu umgehen.

- 1. Lösung: Alle Divisionen werden durch einen Funktionsaufruf ersetzt. Als erstes wird eine Testdivision durchgeführt mit den Werten, die bei der Rechnung x\*(1/x)=1 nicht das richtige Ergebnis haben, um zu testen, ob die CPU fehlerhaft ist. Wenn das Ergebnis richtig ist, wird die Division ganz normal durch geführt. Andernfalls wird der Zähler und Nenner der Division mit 3/4 multipliziert. Danach tritt der Fehler nicht mehr auf, da dann der Divisionsalgorithmus nicht mehr auf die fehlerhaften Zellen zugreifen muss.

- 2. Lösung: Ist eine optimierte Variante der ersten Lösung, wo auch getestet wird ob die CPU fehlerhaft ist, und dann Zähler und Nenner mit 3 multipliziert werden, was auch den Fehler behebt. Vorteil dieser Variante ist, dass die Multiplikation mit 3 erheblich schneller ist als die Multiplikation mit 3/4.<sup>28</sup>

- 3. Lösung: Die FPU wird komplett deaktiviert.

Die ersten beiden Lösungen sind eigentlich nur für Projekte möglich, die gerade programmiert werden und wo eine solche Funktion in das aktuelle Projekt eingebunden werden kann. Für bereits verkaufte Programme müssten Patches nachgereicht werden, was mit einem erheblichen Aufwand verbunden wäre und immense Kosten für die Softwarehersteller zufolge hätte, obwohl diese nicht die Verursacher des Fehlers sind. Also müssten die Softwarefirmen für den Fehler von Intel bezahlen. Zudem wird durch die Abfrage vor der Division die gesamte Division um 20-30% langsamer.<sup>29</sup>

$<sup>^{28}</sup>$  Moler, C., 1994: A New Hardware/Software Pentium FDIV Workaround, online im Internet unter: http://web.ccr.jussieu.fr/ccr/Documentation/Calcul/matlab5v11/docs/00001/001ad.txt [letzter Zugriff: 17.02.2004]

<sup>&</sup>lt;sup>29</sup>McClain, D. & Lyons, P.J., 1994: Slow, Division ahead, The New York Times, online im Internet unter: http://web.ccr.jussieu.fr/ccr/Documentation/Calcul/matlab5v11/docs/00001/001bd.gif [letzter Zugriff: 17.02.2003]

Die dritte Lösung ist theoretisch für jeden Endanwender durchführbar, nur durch das Deaktivieren der FPU des Pentium Prozessor wird dieser um bis zu 90% langsamer, was zur Folge hätte, dass ein Pentium CPU, ohne FPU langsamer laufen würde als ein 486er.

# Reaktionen der Öffentlichkeit und Geschäftspartner

Während Intel sich weiterhin nicht bereit erklärte, alle fehlerhaften Pentium CPUs auszutauschen, wuchs die Kritik an Intels "Kundenfreundlichkeit"stetig. Als Reaktion auf Intels Statistik zur Häufigkeit des Fehlers veröffentlichte IBM ebenfalls eine eigene Statistk, die besagte, dass der Fehler alle 24 Tage einmal auf jeden PC mit Pentium Prozessor auftreten würde. Bei dieser Statistik ging IBM von der Annahme aus, dass ein durchschnittlicher PC etwa 4,2 Millionen Divisionen pro Tag durchführt. Intel dagegen war von 1.000 Divisionen am Tag ausgegangen.

Die Firma Compuserve veröffentlichte ebenfalls eine Statistik zu der Häufigkeit des Fehlers, deren Ergebniss in etwa zwischen den Ergebnisse von Intel und IBM lag und im Groben der tatsächlichen Häufigkeit des Fehlers entsprach.

Als sich Intel weiterhin nicht einsichtig zeigte und auch weiterhin die fehlerhaften Prozessoren auslieferte, gab IBM bekannt, dass ab sofort keine PC-Systeme mit Intel-Pentium Prozessoren mehr von IBM ausgeliefert werden würden. Dieses Vorhaben konnte aber IBM nicht lange durchsetzen, weil IBM viel zu viele Pentium-Systeme verkaufte und es schließlich keine Konkurrenzprodukte zum Intel Pentium gab. Außerdem besaß IBM selbst sehr viele Pentium CPUs, die in die Systeme eingebaut werden sollten. IBM hatte damit gerechnet, dass andere Computerhersteller wie zum Beispiel Compag sich IBM anschießen würden. Compaq und viele andere Computerhersteller stellten sich aber statt dessen hinter Intel und versuchten den Kunden klarzumachen, das der Fehler nicht schwerwiegend sei. Hintergrund dieser Beschwichtigungskampagne waren letztendlich die drohenden Kosten, die durch das Umtauschen aller bisher ausgelieferten Pentium Prozessoren entstehen würden. Da die Bekanntheit des Fehlers in der Pentium CPU erheblich durch Presse und Internet zugenommen hatte, war die Kundenhotline von Intel mit nahezu 10.000 Anrufen pro Tag überlastet. Schließlich waren schon über 2 Millionen fehlerhafte Pentim CPUs verkauft worden.<sup>30</sup>

<sup>&</sup>lt;sup>30</sup>vgl. Jackson, T., 1998, a.a.O., Seite 7 ff. & Seite 433 ff.

#### Intels Konkurrenz

Intels Konkurrenten konnten aus dem Debakel von Intel mit dem fehlerhaften Pentium Prozessor kaum Kapital schlagen, geschweige denn Marktanteile gewinnen.

#### 8.1 AMD

AMD war noch mit der Entwicklung des 5x86er (Auslieferung begann in der 11. Kalenderwoche 1995) beschäftigt, der sozusagen ein Pentium-Konkurrenzprodukt zum Intel Pentium auf 486er Systemen werden sollte. Und der K5, der auf der Pentium-Basis die Konkurrenz sein sollte war auch noch lange nicht fertig und wurde erst in der 6. Kalenderwoche 1996 erstmals ausgeliefert.<sup>31</sup> Der 5x86er und der K5 kamen beide zu spät auf den Markt. Als der 5x86er auf den Markt kam, waren schon sehr viele PC-Besitzer auf Pentium-Systeme umgestiegen und hatten kein 486er Motherboard um diese CPU einzusetzen. Außerdem war dieser Prozessor nur bedingt konkurrenzfähig in Puncto Geschwindigkeit. AMD hatte zwar ein sogenanntes Pentium-Rating eingeführt, demzufolge der 5x86er mit einem Pentium P54C mit 75 MHz ebenbürtig sein sollte. Effektiv konnte der AMD Prozessorn nur bei Officeanwendung vergleichbat schnell arbeiten. Bei Multimediaanwendungen, die vermehrt Fließkommaberechnungen fordern war der AMD Prozessor viel langsamer, trotz eines reellen Taktes von 133 MHz. Der K5 dagegen hat bei einigen Varianten einen reell einen niedrigeren Takt als der nach dem Pentium-Rating äquivaltente Pentium Prozessor. So wurde eine Variante des K5 mit dem Pentium Rating 133 stattdessen nur mit 100 MHz getaktet. In einigen Bereichen war der K5 den entsprechenden Pentium Prozessoren ebenbürtig, wurde aber ebenfalls wie der 5x86er deklassiert, wenn Fließkommazahlen berechnet werden sollten.<sup>32</sup>

$<sup>^{31} \</sup>mathrm{vgl.}$  CPU-Museum, 2002 - 2003 f: AMD 5x86, online im Internet unter: http://www.cpu-museum.de/?m=AMD&f=5x86 [letzter Zugriff: 30.08.2003]

$<sup>^{32}</sup>$ vgl. Dr. Dobb's Journal , 2003, a.a.O.

#### 8.2 Cyrix & andere CPU-Hersteller

Cyrix hatte sich auch noch lange auf das Geschäft mit den 486ern konzentriert und hatte dementsprechend noch kein fertig entwickeltes Konkurrenzprodukt. Der Cyrix 5x86er hatte zwar eine sehr ausgereifte Architektur, konnte aber trotzdem nur bedingt mit äquivalent eingestuften Intel Prozessoren mithalten. Der 5x86er von Cyrix wurde erstmals in der 8. Kalenderwoche 1995 ausgeliefert und kam somit erst nachdem Intel das Debakel mit dem Pentium-Bug abgewendet hatte auf den Markt.<sup>33</sup>

IDT, WinChip, VIA und die vielen anderen noch kleineren Prozessorentwickler waren gar nicht im Stande, ein derart komplexes Konkurrenzprodukt rechtzeitig zu entwickeln.

$<sup>\</sup>overline{\ \ ^{33}\text{CPU-Museum},\ 2002}$ - 2003 e: Cyrix 5x86, online im Internet unter: http://www.cpu-museum.de/?m=Cyrix&f=5x86 [letzter Zugriff: 30.08.2003]

# Intels Konsequenzen

#### 9.1 Umtausch

Aufgrund des ernormen öffentlichen Drucks auf Intel sicherte Intel schließlich doch zu, alle fehlerhaften Pentium CPUs auszutauschen, und es wurde eine eigene Hotline-Abteilung allein für die Betreung der Kunden mit fehlerhaften Pentium-CPUs eingerichtet. Damit aber der Kunde einen neuen fehlerfreien Pentium Prozessor erhielt, musste dieser Intel eine Kreditkarteneinzugsermächtigung in Höhe von 1.000 US \$ gewähren, falls der Kunde die fehlerhafte CPU nicht an Intel zurücksenden würde. Der Preis einer Pentium CPU lag damals bei 800 bis 900 US \$. Probleme mit dem Umtausch der CPUs wurde, nicht bekannt. 34

#### 9.2 Öffentlichkeitsarbeit

Zusätzlich veröffentlichte Intel Beschreibungen, der in der Pentium CPU enthaltenen Fehler und eine Information darüber, welche Prozessoren von diesem Fehler betroffen waren. Anhand dieser Liste konnte theoretisch jeder, der den Kühler der Pentium CPU entfernte, nachvollziehen, ob eine Pentium CPU mit dem Divisionfehler im System verbaut wurde. Jede CPU ist mit Serienund Produktionsreihen-Nummern ausgestattet, mit denen man in der von Intel veröffentlichte Tabelle herausfinden konnte, ob der Divisionsfehler oder noch andere Fehler in dieser CPU waren.<sup>35</sup>

$<sup>^{34}\</sup>mathrm{vgl.}$  Jackson, T., 1998, a.a.O., Seite 435 ff.

<sup>&</sup>lt;sup>35</sup>vgl. Jackson, T., 1998, a.a.O., Seite 436 f.

Diese Pentium CPU mit 75 MHz hat die Produktionsreihennummer SX961. Diese Nummer befindet sich in der Regel am Ende der ersten Zeile der Angaben auf der CPU. Aber auch eine genaue Beschreibung und Aufschlüsselung aller auf der CPU befindlichen Daten wurde von Intel in den Spezifikationsblättern veröffentlicht. Die CPUs der Produktionsreihe SX961 waren bereits fehlerfrei.

$<sup>\</sup>overline{\rm ^{36}CPU\text{-}Abbildungen}$ aus eigener Sammlung

## Verifikation

Intel hatte aus dem Debakel eindeutig gelernt, dass es nicht sinnvoll ist, bekannte Fehler geheim zu halten. Statt dessen wurde dazu übergegangen, dass Listen mit Fehlern und Problemen der CPUs veröffentlicht wurden. Dadurch kamen zwar viele der Öffentlichkeit noch unbekannte Fehler zum Vorschein, aber das Vertrauen der Kunden erlangte Intel damit zurück und setze zugleich seine Konkurrenz unter Druck, ähnliche Fehlerbeschreibungen für die eigenen Produkte zu veröffentlichen. Intel hatte es sozusagen geschafft, aus der Not heraus einen neuen Qualitätsstandard im Bereich der CPU-Vermarktung zu setzen.<sup>37</sup>

Im Bereich der firmeninternen Verifikation der Produkte wurde bei Intel in Zukunft sorgfältiger gearbeitet. So wurden auch die grundlegenden Richtlinien von G.J. Myers<sup>38</sup> bei der Entwicklung von Produkten berücksichtigt.

- "Programmierer sollten nicht den Abnahmetest ihrer eigenen Programme durchführen!

- Die Softwareerstellungsgruppe sollte nicht für die Qualitätssicherung verantwortlich sein!

- Überprüfe die Ergebnisse der Tests gründlich!

- Teste nach gültigen und erwarteten Resultaten ebenso wie nach ungültigen und erwarteten Resultaten

- Teste, ob ein Programm das tut, was es soll, und ebenso, ob es nicht tut, was es nicht soll!

- Plane keinen Test unter der Annahme, das Programm sei jetzt fehlerfrei."

Die Verifikation von entwickelten Produktenn beansprucht meist um die 50% der Entwicklungszeit und -kosten.

$<sup>^{37}\</sup>mathrm{vgl.}$  Jackson, T., 1998, a.a.O., Seite 434

<sup>&</sup>lt;sup>38</sup>Myers, G.J., 1989: Methodisches Testen von Programmen, München, R. Oldenbourg

## Schaden

Der finanzielle Schaden für Intel belief sich auf ca. 475 Millionen US \$, dabei wird angenommen, dass diese Zahl sich nur auf die Kosten für den Austausch der im Umlauf befindlichen CPUs und den Absatzverlust durch den Imageverlust bezieht. Insgesamt wurden mehr als 2 Millionen fehlerhafte CPUs an Endkunden verkauft. Insgesamt musste Intel 500.000 Pentium Prozessoren in den eigenen Lagerbeständen verschrotten und weitere 1,5 Millionen, die von Händlern zurückgesendet wurden. Wieviele CPUs Intel von Endkunden ausgetauscht hat wurde nie veröffentlicht; Schätzungen der New York Times zufolge wurden auf dem amerikanischen Markt insgesamt nur ca. 10% der fehlerhaften CPUs aus Industrie und Forschung umgetauscht und nur ca. 2% der fehlerhaften CPUs aus den Systemen der Heimanwender. Für den europäischen Markt lassen sich ähnliche Werte annehmen. Demzufolge hat sich der Schaden aufgrund der nur sehr wenigen umgetauschten CPUs für Intel sehr im Rahmen gehalten. Zum Vergleich belief sich der Gewinn von Intel im 4. Quartal 1994 auf ca. 850 Millionen US \$.39

<sup>&</sup>lt;sup>39</sup>vgl. Jackson, T., 1998, a.a.O., Seite 427 ff.

#### **Fazit**

Es ist nicht mehr möglich, fehlerfreie CPUs zu produzieren. Grund dafür sind sowohl die ständig steigende Instruktionsvielfalt als auch die immer weiter steigende Komplexität der aktuellen CPUs. Es werden mittlerweile über 50 Millionen Transistoren auf engsten Raum geätzt und mehrere verschieden Instruktionseinheiten auf den CPUs untergebracht. Deshalb wurde die Verifikation der CPUs für die Hersteller umso wchtiger, da es darum geht, möglichst alle schwerwiegenden Fehler in den CPUs soweit wie möglich ausschließen zu können. Für einige Fehler ist es auch möglich, Workarounds in einen EPROM (Eraseable Programmable Read Only Memory) auf der CPU nachträglich zu programmieren oder Workarounds auf Betriebssystemebene zu installieren. Die Pentium Prozessoren enthalten bis zu 100 Fehler, die zum Teil wegen eines sehr geringen Auftretens in ganz speziellen Fällen nie korrigiert wurden. Dies war auch nur möglich, weil Intel bald eine pinkompatible Weiterentwicklung des P54C auf den Markt brachte, den P55C, der erstmals die Multimediaerweiterung MMX enthielt.

Außerdem können die CPU-Hersteller auch nicht im vorraus alle Inkompatibilitäten mit allen Hardwareprodukten ausschließen. Dazu ist das Angebot an Hardwarekomponenten auf dem PC-Markt viel zu vielfältig und es kann nicht die Entwicklung anderer Hardwarekomponenten berücksichtigt werden. Im Allgemeinen müssen alle Hardwarehersteller darauf achten, dass sie ihre jeweiligen Produkte so kompatibel wie möglich zu allen möglichen anderen Produkten halten. So gab es einige Zeit oft Probleme mit dem Platinenlayout und den auf dem Markt erhältlichen CPU-Kühlern. Die CPU-Kühler konnten auf der CPU nicht angebracht werden, weil sich die Motherboard-Hersteller nicht auf den steigenden Kühlungsbedarf der Prozessoren eingestellt hatten und nicht damit gerechnet hatten, dass in absehbarer Zeit CPU-Kühler notwendig werden würden, die eine größere Fläche als die CPU selber abdecken würden. So waren oft relativ große Kondensatoren zu nah am CPU-Sockel angebracht, so dass diese eine Montage des CPU-Kühlers verhinderten.

## Literatur

- Bernstein H., 1991: PC-TUNING Vom Standard-PC zum Personal-Super-Computer, München: Markt & Technik Verlag

- **Bryant, R.E.,** 1998: Implementing Computer Arithmetics, online im Internet unter:

http://www.cs.cmu.edu/afs/cs.cmu.edu/academic/class/ 15347-s98/public/lectures/lect05.pdf [letzter Zugriff: 15.06.2003]

- CPU-Museum, 2002 2003 a: Intel 8086, online im Internet unter: http://www.cpu-museum.de/?m=Intel&f=8086 [letzter Zugriff: 30.08.2003]

- CPU-Museum, 2002 2003 b: Intel Pentium P5, online im Internet unter: http://www.cpu-museum.de/?m=Intel&f=Pentium+P5 [letzter Zugriff: 30.08.2003]

- CPU-Museum, 2002 2003 c: Intel Pentium P54C, online im Internet unter: http://www.cpu-museum.de/?m=Intel&f=Pentium-S+%2F+P54C[letzter Zugriff: 30.08.2003]

- CPU-Museum, 2002 2003 d: Intel 486DX, online im Internet unter: http://www.cpu-museum.de/?m=Intel&f=80486DX [letzter Zugriff: 30.08.2003]

- CPU-Museum, 2002 2003 e: Cyrix 5x86, online im Internet unter: http://www.cpu-museum.de/?m=Cyrix&f=5x86 [letzter Zugriff: 30.08.2003]

- CPU-Museum, 2002 2003 f: AMD 5x86, online im Internet unter: http://www.cpu-museum.de/?m=AMD&f=5x86 [letzter Zugriff: 30.08.2003]

- Dr. Dobb's Journal, 2003: PC Processors Guide by x86.org, online im Internet unter:http://x86.ddj.com/articles/computalk/help.htm [letzter Zugriff: 07.05.2003]

- Fog, A., 2003: Branch prediction in the Pentium family, online im Internet unter: http://x86.ddj.com/articles/branch/branchprediction.htm[letzter Zugriff: 01.07.2003]

- Gardner, A., 1993: Beck EDV-Berater im dtv Basiswissen: PC-Hardware Rechner Tastatur Maus Bildschirm Disketten, 2. Auflage, München, Verlag C.H. Beck

- Gelsinger, P.P., 2003: For ever young. Die Intel-Architektur: 25 Jahre Innovation und kein Ende abzusehen, in: c't Magazin für Computer und Technik, Ausgabe 13/2003, S. 92 95

- **Grove**, **A.S.**, 1999: Nur die Paranoiden überleben Strategische Wendepunkte vorzeitig erkennen, München, Wilhelm Heyne Verlag

- Halfhill, T.R., 1995: The Truth Behind The Bug, online im Internet unter: http://www.byte.com/art/9503/sec13/art1.htm[letzter Zugriff: 03.07.2003]

- Intel Corporation, 1994: Statistical Analysis of Floating Point Flaw in the Pentium Processor (Dateiname: Intel\_white.ps), in: pentium.zip, Download unter:

- Intel Corporation, 1997 a: 60- and 66-MHz Pentium Processor Specification Update. Order Number: 243326-001, online im Internet unter: http://www.intel.com/design/intorch/specupdt/fhb.pdf [letzter Zugriff am 27.08.2003]

- Intel Corporation, 1997 b: Pentium Processor, online im Internet unter:

http://developer.intel.com/design/pentium/datashts/24199710.pdf

[letzter Zugriff: 17.02.2004]

- Intel Corporation, 1999: Pentium Processor Specification Update. Order Number: 242480-041, online im Internet unter: http://www.intel.com/design/intorch/specupdt/24248041.pdf [letz-ter Zugriff: 27.08.2003]

- Jackson, T., 1998: Inside Intel Die Geschichte des erfolgreichsten Chip-Produzenten der Welt, Hamburg, Hoffmann und Campe Verlag

- McClain, D. & Lyons, P.J., 1994: Slow, Division ahead, The New York Times, online im Internet unter:

http://web.ccr.jussieu.fr/ccr/Documentation/Calcul/

matlab5v11/docs/00001/001bd.gif [letzter Zugriff: 17.02.2003]

- Moler, C., 1994: A New Hardware/Software Pentium FDIV Workaround, online im Internet unter: http://web.ccr.jussieu.fr/ccr/Documentation/Calcul/

- matlab5v11/docs/00001/001ad.txt [letzter Zugriff: 17.02.2004]

- Myers, G.J., 1989: Methodisches Testen von Programmen, München, R. Oldenbourg

- www.bigtom.ch, 2003: CPU-Chronik, online im Internet unter: http://www.bigtom.ch/CPUs/index5.htm [letzter Zugriff: 14.06.2003]